# **Op Amps For Everyone**

Ron Mancini, Editor in Chief

# Design Reference

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

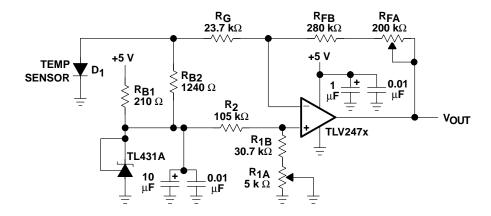

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of that third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

# The Op Amp's Place In The World

### Ron Mancini

In 1934 Harry Black[1] commuted from his home in New York City to work at Bell Labs in New Jersey by way of a railroad/ferry. The ferry ride relaxed Harry enabling him to do some conceptual thinking. Harry had a tough problem to solve; when phone lines were extended long distances, they needed amplifiers, and undependable amplifiers limited phone service. First, initial tolerances on the gain were poor, but that problem was quickly solved with an adjustment. Second, even when an amplifier was adjusted correctly at the factory, the gain drifted so much during field operation that the volume was too low or the incoming speech was distorted.

Many attempts had been made to make a stable amplifier, but temperature changes and power supply voltage extremes experienced on phone lines caused uncontrollable gain drift. Passive components had much better drift characteristics than active components had, thus if an amplifier's gain could be made dependent on passive components, the problem would be solved. During one of his ferry trips, Harry's fertile brain conceived a novel solution for the amplifier problem, and he documented the solution while riding on the ferry.

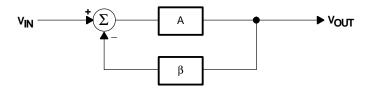

The solution was to first build an amplifier that had more gain than the application required. Then some of the amplifier output signal was fed back to the input in a manner that makes the circuit gain (circuit is the amplifier and feedback components) dependent on the feedback circuit rather than the amplifier gain. Now the circuit gain is dependent on the passive feedback components rather than the active amplifier. This is called negative feedback, and it is the underlying operating principle for all modern day op amps. Harry had documented the first intentional feedback circuit during a ferry ride. I am sure unintentional feedback circuits had been built prior to that time, but the designers ignored the effect!

I can hear the squeals of anguish coming from the managers and amplifier designers. I imagine that they said something like this, "it is hard enough to achieve 30-kHz gain—bandwidth (GBW), and now this fool wants me to design an amplifier with 3-MHz GBW. But, he is still going to get a circuit gain GBW of 30 kHz". Well, time has proven Harry right, but there is a minor problem that Harry didn't discuss in detail, and that is the oscillation

problem. It seems that circuits designed with large open loop gains sometimes oscillate when the loop is closed. A lot of people investigated the instability effect, and it was pretty well understood in the 1940s, but solving stability problems involved long, tedious, and intricate calculations. Years passed without anybody making the problem solution simpler or more understandable.

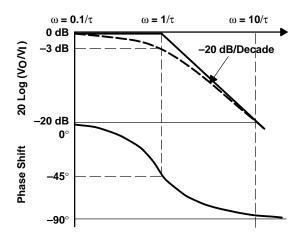

In 1945 H. W. Bode presented a system for analyzing the stability of feedback systems by using graphical methods. Until this time, feedback analysis was done by multiplication and division, so calculation of transfer functions was a time consuming and laborious task. Remember, engineers did not have calculators or computers until the '70s. Bode presented a log technique that transformed the intensely mathematical process of calculating a feedback system's stability into graphical analysis that was simple and perceptive. Feedback system design was still complicated, but it no longer was an art dominated by a few electrical engineers kept in a small dark room. Any electrical engineer could use Bode's methods to find the stability of a feedback circuit, so the application of feedback to machines began to grow. There really wasn't much call for electronic feedback design until computers and transducers become of age.

The first real-time computer was the analog computer! This computer used preprogrammed equations and input data to calculate control actions. The programming was hard wired with a series of circuits that performed math operations on the data, and the hard wiring limitation eventually caused the declining popularity of the analog computer. The heart of the analog computer was a device called an operational amplifier because it could be configured to perform many mathematical operations such as multiplication, addition, subtraction, division, integration, and differentiation on the input signals. The name was shortened to the familiar *op amp*, as we have come to know and love them. The op amp used an amplifier with a large open loop gain, and when the loop was closed, the amplifier performed the mathematical operations dictated by the external passive components. This amplifier was very large because it was built with vacuum tubes and it required a high-voltage power supply, but it was the heart of the analog computer, thus its large size and huge power requirements were accepted as the price of doing business. Many early op amps were designed for analog computers, and it was soon found out that op amps had other uses and were very handy to have around the physics lab.

At this time general-purpose analog computers were found in universities and large company laboratories because they were critical to the research work done there. There was a parallel requirement for transducer signal conditioning in lab experiments, and op amps found their way into signal conditioning applications. As the signal conditioning applications expanded, the demand for op amps grew beyond the analog computer requirements, and even when the analog computers lost favor to digital computers, the op amp survived because of its importance in universal analog applications. Eventually digital computers replaced the analog computers (a sad day for real-time measurements), but the demand for op amps increased as measurement applications increased.

The first signal conditioning op amps were constructed with vacuum tubes prior to the introduction of transistors, so they were large and bulky. During the '50s, miniature vacuum tubes that worked from lower voltage power supplies enabled the manufacture of op amps that shrunk to the size of a brick used in house construction, so the op amp modules were nicknamed *bricks*. Vacuum tube size and component size decreased until an op amp was shrunk to the size of a single octal vacuum tube. Transistors were commercially developed in the '60s, and they further reduced op amp size to several cubic inches, but the nickname brick still held on. Now the nickname brick is attached to any electronic module that uses potting compound or non-integrated circuit (IC) packaging methods. Most of these early op amps were made for specific applications, so they were not necessarily general purpose. The early op amps served a specific purpose, but each manufacturer had different specifications and packages; hence, there was little second sourcing among the early op amps.

ICs were developed during the late 1950s and early 1960s, but it wasn't till the middle 1960s that Fairchild released the  $\mu$ A709. This was the first commercially successful IC op amp, and Robert J. Widler designed it. The  $\mu$ A709 had its share of problems, but any competent analog engineer could use it, and it served in many different analog applications. The major drawback of the  $\mu$ A709 was stability; it required external compensation and a competent analog engineer to apply it. Also, the  $\mu$ A709 was quite sensitive because it had a habit of self destructing under any adverse condition. The self-destruction habit was so prevalent that one major military equipment manufacturer published a paper titled something like, *The 12 Pearl Harbor Conditions of the*  $\mu$ A709. The  $\mu$ A741 followed the  $\mu$ A709, and it is an internally compensated op amp that does not require external compensation if operated under data sheet conditions. Also, it is much more forgiving than the  $\mu$ A709. There has been a never-ending series of new op amps released each year since then, and their performance and reliability has improved to the point where present day op amps can be used for analog applications by anybody.

The IC op amp is here to stay; the latest generation op amps cover the frequency spectrum from 5-kHz GBW to beyond 1-GHz GBW. The supply voltage ranges from guaranteed operation at 0.9 V to absolute maximum voltage ratings of 1000 V. The input current and input offset voltage has fallen so low that customers have problems verifying the specifications during incoming inspection. The op amp has truly become the universal analog IC because it performs all analog tasks. It can function as a line driver, comparator (one bit A/D), amplifier, level shifter, oscillator, filter, signal conditioner, actuator driver, current source, voltage source, and many other applications. The designer's problem is how to rapidly select the correct circuit/op amp combination and then, how to calculate the passive component values that yield the desired transfer function in the circuit.

This book deals with op amp circuits — not with the innards of op amps. It treats the calculations from the circuit level, and it doesn't get bogged down in a myriad of detailed calculations. Rather, the reader can start at the level appropriate for them, and quickly move on to the advanced topics. If you are looking for material about the innards of op amps

you are looking in the wrong place. The op amp is treated as a completed component in this book.

The op amp will continue to be a vital component of analog design because it is such a fundamental component. Each generation of electronics equipment integrates more functions on silicon and takes more of the analog circuitry inside the IC. Don't fear, as digital applications increase, analog applications also increase because the predominant supply of data and interface applications are in the real world, and the real world is an analog world. Thus, each new generation of electronics equipment creates requirements for new analog circuits; hence, new generations of op amps are required to fulfill these requirements. Analog design, and op amp design, is a fundamental skill that will be required far into the future.

### References

1 Black, H. S., Stabilized Feedback Amplifiers, BSTJ, Vol. 13, January 1934

# **Review of Circuit Theory**

#### Ron Mancini

### 2.1 Introduction

Although this book minimizes math, some algebra is germane to the understanding of analog electronics. Math and physics are presented here in the manner in which they are used later, so no practice exercises are given. For example, after the voltage divider rule is explained, it is used several times in the development of other concepts, and this usage constitutes practice.

Circuits are a mix of passive and active components. The components are arranged in a manner that enables them to perform some desired function. The resulting arrangement of components is called a circuit or sometimes a circuit configuration. The art portion of analog design is developing the circuit configuration. There are many published circuit configurations for almost any circuit task, thus all circuit designers need not be artists.

When the design has progressed to the point that a circuit exists, equations must be written to predict and analyze circuit performance. Textbooks are filled with rigorous methods for equation writing, and this review of circuit theory does not supplant those textbooks. But, a few equations are used so often that they should be memorized, and these equations are considered here.

There are almost as many ways to analyze a circuit as there are electronic engineers, and if the equations are written correctly, all methods yield the same answer. There are some simple ways to analyze the circuit without completing unnecessary calculations, and these methods are illustrated here.

### 2.2 Laws of Physics

Ohm's law is stated as V=IR, and it is fundamental to all electronics. Ohm's law can be applied to a single component, to any group of components, or to a complete circuit. When the current flowing through any portion of a circuit is known, the voltage dropped across that portion of the circuit is obtained by multiplying the current times the resistance (Equation 2–1).

$$V = IR (2-1)$$

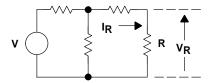

In Figure 2–1, Ohm's law is applied to the total circuit. The current, (I) flows through the total resistance (R), and the voltage (V) is dropped across R.

Figure 2-1. Ohm's Law Applied to the Total Circuit

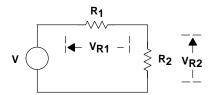

In Figure 2–2, Ohm's law is applied to a single component. The current ( $I_R$ ) flows through the resistor (R) and the voltage ( $V_R$ ) is dropped across R. Notice, the same formula is used to calculate the voltage drop across R even though it is only a part of the circuit.

Figure 2-2. Ohm's Law Applied to a Component

Kirchoff's voltage law states that the sum of the voltage drops in a series circuit equals the sum of the voltage sources. Otherwise, the source (or sources) voltage must be dropped across the passive components. When taking sums keep in mind that the sum is an algebraic quantity. Kirchoff's voltage law is illustrated in Figure 2–3 and Equations 2–2 and 2–3.

Figure 2–3. Kirchoff's Voltage Law

$$\sum V_{SOURCES} = \sum V_{DROPS}$$

(2-2)

$$V = V_{R1} + V_{R2} (2-3)$$

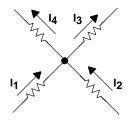

Kirchoff's current law states: the sum of the currents entering a junction equals the sum of the currents leaving a junction. It makes no difference if a current flows from a current

source, through a component, or through a wire, because all currents are treated identically. Kirchoff's current law is illustrated in Figure 2–4 and Equations 2–4 and 2–5.

Figure 2-4. Kirchoff's Current Law

$$\sum I_{IN} = \sum I_{OUT}$$

(2-4)

$$I_1 + I_2 = I_3 + I_4$$

(2-5)

### 2.3 Voltage Divider Rule

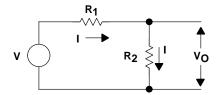

When the output of a circuit is not loaded, the voltage divider rule can be used to calculate the circuit's output voltage. Assume that the same current flows through all circuit elements (Figure 2–5). Equation 2–6 is written using Ohm's law as  $V = I(R_1 + R_2)$ . Equation 2–7 is written as Ohm's law across the output resistor.

Figure 2–5. Voltage Divider Rule

$$I = \frac{V}{R_1 + R_2} \tag{2-6}$$

$$V_{OUT} = IR_2 \tag{2-7}$$

Substituting Equation 2–6 into Equation 2–7, and using algebraic manipulation yields Equation 2–8.

$$V_{OUT} = V \frac{R_2}{R_1 + R_2}$$

(2-8)

A simple way to remember the voltage divider rule is that the output resistor is divided by the total circuit resistance. This fraction is multiplied by the input voltage to obtain the output voltage. Remember that the voltage divider rule always assumes that the output resistor is not loaded; the equation is not valid when the output resistor is loaded by a parallel component. Fortunately, most circuits following a voltage divider are input circuits, and input circuits are usually high resistance circuits. When a fixed load is in parallel with the output resistor, the equivalent parallel value comprised of the output resistor and loading resistor can be used in the voltage divider calculations with no error. Many people ignore the load resistor if it is ten times greater than the output resistor value, but this calculation can lead to a 10% error.

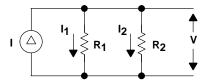

### 2.4 Current Divider Rule

When the output of a circuit is not loaded, the current divider rule can be used to calculate the current flow in the output branch circuit ( $R_2$ ). The currents  $I_1$  and  $I_2$  in Figure 2–6 are assumed to be flowing in the branch circuits. Equation 2–9 is written with the aid of Kirchoff's current law. The circuit voltage is written in Equation 2–10 with the aid of Ohm's law. Combining Equations 2–9 and 2–10 yields Equation 2–11.

Figure 2–6. Current Divider Rule

$$I = I_1 + I_2 \tag{2-9}$$

$$V = I_1 R_1 = I_2 R_2 (2-10)$$

$$I = I_1 + I_2 = I_2 \frac{R_2}{R_1} + I_2 = I_2 \left( \frac{R_1 + R_2}{R_1} \right)$$

(2-11)

Rearranging the terms in Equation 2–11 yields Equation 2–12.

$$I_2 = I \left( \frac{R_1}{R_1 + R_2} \right) \tag{2-12}$$

The total circuit current divides into two parts, and the resistance ( $R_1$ ) divided by the total resistance determines how much current flows through  $R_2$ . An easy method of remembering the current divider rule is to remember the voltage divider rule. Then modify the voltage divider rule such that the opposite resistor is divided by the total resistance, and the fraction is multiplied by the input current to get the branch current.

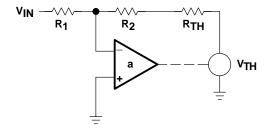

### 2.5 Thevenin's Theorem

There are times when it is advantageous to isolate a part of the circuit to simplify the analysis of the isolated part of the circuit. Rather than write loop or node equations for the complete circuit, and solving them simultaneously, Thevenin's theorem enables us to isolate the part of the circuit we are interested in. We then replace the remaining circuit with a simple series equivalent circuit, thus Thevenin's theorem simplifies the analysis.

There are two theorems that do similar functions. The Thevenin theorem just described is the first, and the second is called Norton's theorem. Thevenin's theorem is used when the input source is a voltage source, and Norton's theorem is used when the input source is a current source. Norton's theorem is rarely used, so its explanation is left for the reader to dig out of a textbook if it is ever required.

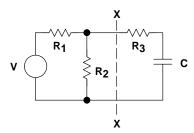

The rules for Thevenin's theorem start with the component or part of the circuit being replaced. Referring to Figure 2–7, look back into the terminals (left from C and  $R_3$  toward point XX in the figure) of the circuit being replaced. Calculate the no load voltage ( $V_{TH}$ ) as seen from these terminals (use the voltage divider rule).

Figure 2–7. Original Circuit

Look into the terminals of the circuit being replaced, short independent voltage sources, and calculate the impedance between these terminals. The final step is to substitute the Thevenin equivalent circuit for the part you wanted to replace as shown in Figure 2–8.

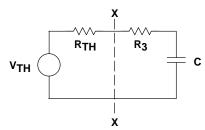

Figure 2–8. Thevenin's Equivalent Circuit for Figure 2–7

The Thevenin equivalent circuit is a simple series circuit, thus further calculations are simplified. The simplification of circuit calculations is often sufficient reason to use Thevenin's

theorem because it eliminates the need for solving several simultaneous equations. The detailed information about what happens in the circuit that was replaced is not available when using Thevenin's theorem, but that is no consequence because you had no interest in it.

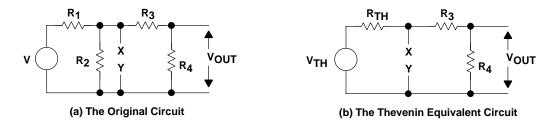

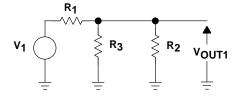

As an example of Thevenin's theorem, let's calculate the output voltage ( $V_{OUT}$ ) shown in Figure 2–9A. The first step is to stand on the terminals X–Y with your back to the output circuit, and calculate the open circuit voltage seen ( $V_{TH}$ ). This is a perfect opportunity to use the voltage divider rule to obtain Equation 2–13.

Figure 2-9. Example of Thevenin's Equivalent Circuit

$$V_{TH} = V \frac{R_2}{R_1 + R_2}$$

(2–13)

Still standing on the terminals X-Y, step two is to calculate the impedance seen looking into these terminals (short the voltage sources). The Thevenin impedance is the parallel impedance of  $R_1$  and  $R_2$  as calculated in Equation 2–14. Now get off the terminals X-Y before you damage them with your big feet. Step three replaces the circuit to the left of X-Y with the Thevenin equivalent circuit  $V_{TH}$  and  $R_{TH}$ .

$$R_{TH} = \frac{R_1 R_2}{R_1 + R_2} = R_1 \| R_2$$

(2-14)

### Note:

Two parallel vertical bars (  $\parallel$  ) are used to indicate parallel components as shown in Equation 2–14.

The final step is to calculate the output voltage. Notice the voltage divider rule is used again. Equation 2–15 describes the output voltage, and it comes out naturally in the form of a series of voltage dividers, which makes sense. That's another advantage of the voltage divider rule; the answers normally come out in a recognizable form rather than a jumble of coefficients and parameters.

$$V_{OUT} = V_{TH} \frac{R_4}{R_{TH} + R_3 + R_4} = V \left(\frac{R_2}{R_1 + R_2}\right) \frac{R_4}{\frac{R_1 R_2}{R_1 + R_2} + R_3 + R_4}$$

(2-15)

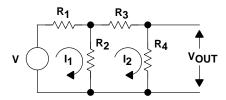

The circuit analysis is done the hard way in Figure 2–10, so you can see the advantage of using Thevenin's Theorem. Two loop currents,  $I_1$  and  $I_2$ , are assigned to the circuit. Then the loop Equations 2–16 and 2–17 are written.

Figure 2-10. Analysis Done the Hard Way

$$V = I_1(R_1 + R_2) - I_2R_2 (2-16)$$

$$I_2(R_2 + R_3 + R_4) = I_1R_2 (2-17)$$

Equation 2–17 is rewritten as Equation 2–18 and substituted into Equation 2–16 to obtain Equation 2–19.

$$I_1 = I_2 \frac{R_2 + R_3 + R_4}{R_2} \tag{2-18}$$

$$V = I_2 \left( \frac{R_2 + R_3 + R_4}{R_2} \right) (R_1 + R_2) - I_2 R_2$$

(2-19)

The terms are rearranged in Equation 2–20. Ohm's law is used to write Equation 2–21, and the final substitutions are made in Equation 2–22.

$$I_2 = \frac{V}{\frac{R_2 + R_3 + R_4}{R_2} (R_1 + R_2) - R_2}$$

(2-20)

$$V_{OUT} = I_2 R_4 \tag{2-21}$$

$$V_{OUT} = V \frac{R_4}{\frac{\left(R_2 + R_3 + R_4\right)\left(R_1 + R_2\right)}{R_2} - R_2}$$

(2-22)

This is a lot of extra work for no gain. Also, the answer is not in a usable form because the voltage dividers are not recognizable, thus more algebra is required to get the answer into usable form.

# 2.6 Superposition

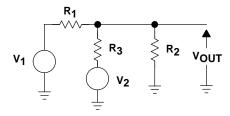

Superposition is a theorem that can be applied to any linear circuit. Essentially, when there are independent sources, the voltages and currents resulting from each source can be calculated separately, and the results are added algebraically. This simplifies the calculations because it eliminates the need to write a series of loop or node equations. An example is shown in Figure 2–11.

Figure 2–11. Superposition Example

When  $V_1$  is grounded,  $V_2$  forms a voltage divider with  $R_3$  and the parallel combination of  $R_2$  and  $R_1$ . The output voltage for this circuit ( $V_{OUT2}$ ) is calculated with the aid of the voltage divider equation (2–23). The circuit is shown in Figure 2–12. The voltage divider rule yields the answer quickly.

Figure 2–12. When V<sub>1</sub> is Grounded

$$V_{OUT2} = V_2 \frac{R_1 \parallel R_2}{R_3 + R_1 \parallel R_2}$$

(2-23)

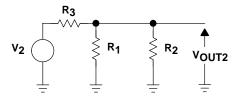

Likewise, when  $V_2$  is grounded (Figure 2–13),  $V_1$  forms a voltage divider with  $R_1$  and the parallel combination of  $R_3$  and  $R_2$ , and the voltage divider theorem is applied again to calculate  $V_{OUT}$  (Equation 2–24).

Figure 2–13. When V<sub>2</sub> is Grounded

$$V_{OUT1} = V_1 \frac{R_2 \| R_3}{R_1 + R_2 \| R_3}$$

(2-24)

After the calculations for each source are made the components are added to obtain the final solution (Equation 2–25).

$$V_{OUT} = V_1 \frac{R_2 \| R_3}{R_1 + R_2 \| R_3} + V_2 \frac{R_1 \| R_2}{R_3 + R_1 \| R_2}$$

(2-25)

The reader should analyze this circuit with loop or node equations to gain an appreciation for superposition. Again, the superposition results come out as a simple arrangement that is easy to understand. One looks at the final equation and it is obvious that if the sources are equal and opposite polarity, and when  $R_1 = R_3$ , then the output voltage is zero. Conclusions such as this are hard to make after the results of a loop or node analysis unless considerable effort is made to manipulate the final equation into symmetrical form.

### 2.7 Calculation of a Saturated Transistor Circuit

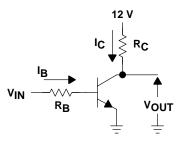

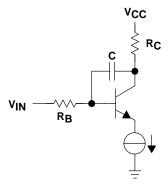

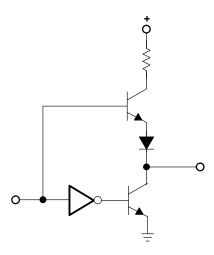

The circuit specifications are: when  $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} < 0.4 \text{ V}$  at  $I_{SINK} < 10 \text{ mA}$ , and  $V_{IN} < 0.05 \text{ V}$ ,  $V_{OUT} > 10 \text{ V}$  at  $I_{OUT} = 1 \text{ mA}$ . The circuit diagram is shown in Figure 2–14.

Figure 2-14. Saturated Transistor Circuit

The collector resistor must be sized (Equation 2–26) when the transistor is off, because it has to be small enough to allow the output current to flow through it without dropping more than two volts to meet the specification for a 10-V output.

$$R_C \le \frac{V_{+12} - V_{OUT}}{I_{OUT}} = \frac{12 - 10}{1} = 2 \text{ k}$$

(2-26)

When the transistor is off, 1 mA can be drawn out of the collector resistor without pulling the collector or output voltage to less than ten volts (Equation 2–27). When the transistor is on, the base resistor must be sized (Equation 2–28) to enable the input signal to drive enough base current into the transistor to saturate it. The transistor beta is 50.

$$I_{C} = \beta I_{B} = \frac{V_{+12} - V_{CE}}{R_{C}} + I_{L} \approx \frac{V_{+12}}{R_{C}} + I_{L}$$

(2-27)

$$R_{B} \le \frac{V_{IN} - V_{BE}}{I_{B}} \tag{2-28}$$

Substituting Equation 2-27 into Equation 2-28 yields Equation 2-29.

$$R_{B} \le \frac{(V_{IN} - V_{BE})\beta}{I_{C}} = \frac{(12 - 0.6)50 \text{ V}}{\left[\frac{12}{2} + (10)\right] \text{ mA}} = 35.6 \text{ k}$$

(2-29)

When the transistor goes on it sinks the load current, and it still goes into saturation. These calculations neglect some minor details, but they are in the 98% accuracy range.

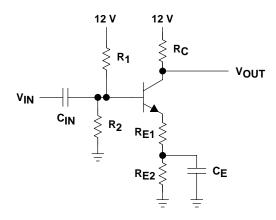

### 2.8 Transistor Amplifier

The amplifier is an analog circuit (Figure 2–15), and the calculations, plus the points that must be considered during the design, are more complicated than for a saturated circuit. This extra complication leads people to say that analog design is harder than digital design (the saturated transistor is digital i.e.; on or off). Analog design is harder than digital design because the designer must account for all states in analog, whereas in digital only two states must be accounted for. The specifications for the amplifier are an ac voltage gain of four and a peak-to-peak signal swing of 4 volts.

Figure 2-15. Transistor Amplifier

$I_C$  is selected as 10 mA because the transistor has a current gain ( $\beta$ ) of 100 at that point. The collector voltage is arbitrarily set at 8 V; when the collector voltage swings positive

2 V (from 8 V to 10 V) there is still enough voltage dropped across R<sub>C</sub> to keep the transistor on. Set the collector-emitter voltage at 4 V; when the collector voltage swings negative 2 V (from 8 V to 6 V) the transistor still has 2 V across it, so it stays linear. This sets the emitter voltage (V<sub>F</sub>) at 4 V.

$$R_C \le \frac{V_{+12} - V_C}{I_C} = \frac{12 V - 8 V}{10 \text{ mA}} = 400 \Omega$$

(2-30)

$$R_E = R_{E1} + R_{E2} = \frac{V_E}{I_E} = \frac{V_E}{I_B + I_C} \cong \frac{V_E}{I_C} = \frac{4 \text{ V}}{10 \text{ mA}} = 400 \Omega$$

(2-31)

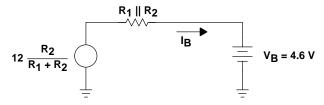

Use Thevenin's equivalent circuit to calculate R<sub>1</sub> and R<sub>2</sub> as shown in Figure 2–16.

Figure 2–16. Thevenin Equivalent of the Base Circuit

$$I_{B} = \frac{I_{C}}{\beta} = \frac{10 \text{ mA}}{100} = 0.1 \text{ mA}$$

(2–32)

$$V_{TH} = \frac{12R_2}{R_1 + R_2} \tag{2-33}$$

$$R_{TH} = \frac{R_1 R_2}{R_1 + R_2} \tag{2-34}$$

We want the base voltage to be 4.6 V because the emitter voltage is then 4 V. Assume a voltage drop of 0.4 V across  $R_{TH}$ , so Equation 2–35 can be written. The drop across  $R_{TH}$  may not be exactly 0.4 V because of beta variations, but a few hundred mV does not matter is this design. Now, calculate the ratio of  $R_1$  and  $R_2$  using the voltage divider rule (the load current has been accounted for).

$$R_{TH} = \frac{0.4}{0.1} k = 4 k \tag{2-35}$$

$$V_{TH} = I_B R_{Th} + V_B = 0.4 + 4.6 = 5 = 12 \frac{R_2}{R_1 + R_2}$$

(2-36)

$$R_2 = \frac{7}{5} R_1 \tag{2-37}$$

$R_1$  is almost equal to  $R_2$ , thus selecting  $R_1$  as twice the Thevenin resistance yields approximately 4 K as shown in Equation 2–35. Hence,  $R_1$  = 11.2 k and  $R_2$  = 8 k. The ac gain is

approximately  $R_C/R_{E1}$  because  $C_E$  shorts out  $R_{E2}$  at high frequencies, so we can write Equation 2–38.

$$R_{E1} = \frac{R_C}{G} = \frac{400}{4} = 100 \Omega$$

(2-38)

$$R_{E2} = R_E - R_{E1} = 400 - 100 = 300 \Omega$$

(2-39)

The capacitor selection depends on the frequency response required for the amplifier, but 10  $\mu$ F for C<sub>IN</sub> and 1000  $\mu$ F for C<sub>E</sub> suffice for a starting point.

# **Development of the Ideal Op Amp Equations**

### Ron Mancini

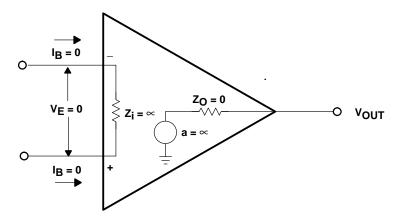

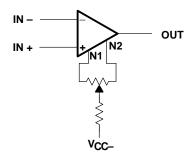

# 3.1 Ideal Op Amp Assumptions

The name *Ideal Op Amp* is applied to this and similar analysis because the salient parameters of the op amp are assumed to be perfect. There is no such thing as an ideal op amp, but present day op amps come so close to ideal that *Ideal Op Amp* analysis approaches actual analysis. Op amps depart from the ideal in two ways. First, dc parameters such as input offset voltage are large enough to cause departure from the ideal. The ideal assumes that input offset voltage is zero. Second, ac parameters such as gain are a function of frequency, so they go from large values at dc to small values at high frequencies.

This assumption simplifies the analysis, thus it clears the path for insight. It is so much easier to see the forest when the brush and huge trees are cleared away. Although the ideal op amp analysis makes use of perfect parameters, the analysis is often valid because some op amps approach perfection. In addition, when working at low frequencies, several kHz, the ideal op amp analysis produces accurate answers. Voltage feedback op amps are covered in this chapter, and current feedback op amps are covered in Chapter 8.

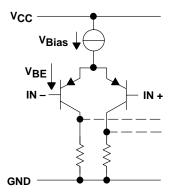

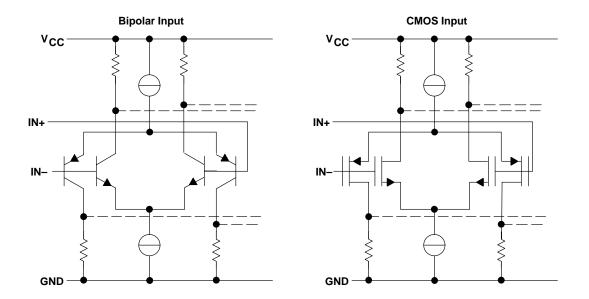

Several assumptions have to be made before the ideal op amp analysis can proceed. First, assume that the current flow into the input leads of the op amp is zero. This assumption is almost true in FET op amps where input currents can be less than a pA, but this is not always true in bipolar high-speed op amps where tens of  $\mu$ A input currents are found.

Second, the op amp gain is assumed to be infinite, hence it drives the output voltage to any value to satisfy the input conditions. This assumes that the op amp output voltage can achieve any value. In reality, saturation occurs when the output voltage comes close to a power supply rail, but reality does not negate the assumption, it only bounds it.

Also, implicit in the infinite gain assumption is the need for zero input signal. The gain drives the output voltage until the voltage between the input leads (the error voltage) is zero. This leads to the third assumption that the voltage between the input leads is zero. The implication of zero voltage between the input leads means that if one input is tied to

a hard voltage source such as ground, then the other input is at the same potential. The current flow into the input leads is zero, so the input impedance of the op amp is infinite.

Fourth, the output impedance of the ideal op amp is zero. The ideal op amp can drive any load without an output impedance dropping voltage across it. The output impedance of most op amps is a fraction of an ohm for low current flows, so this assumption is valid in most cases. Fifth, the frequency response of the ideal op amp is flat; this means that the gain does not vary as frequency increases. By constraining the use of the op amp to the low frequencies, we make the frequency response assumption true.

Table 3–1 lists the basic ideal op amp assumptions and Flgure 3–1shows the ideal op amp.

Table 3-1. Basic Ideal Op Amp Assumptions

| PARAMETER NAME       | PARAMETERS SYMBOL | VALUE |

|----------------------|-------------------|-------|

| Input current        | I <sub>IN</sub>   | 0     |

| Input offset voltage | Vos               | 0     |

| Input impedance      | Z <sub>IN</sub>   | ∞     |

| Output impedance     | Z <sub>OUT</sub>  | 0     |

| Gain                 | а                 | ∞     |

Figure 3-1. The Ideal Op Amp

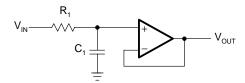

### 3.2 The Noninverting Op Amp

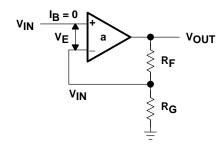

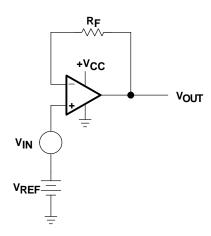

The noninverting op amp has the input signal connected to its noninverting input (Figure 3–2), thus its input source sees an infinite impedance. There is no input offset voltage because  $V_{OS} = V_E = 0$ , hence the negative input must be at the same voltage as the positive input. The op amp output drives current into  $R_F$  until the negative input is at the voltage,  $V_{IN}$ . This action causes  $V_{IN}$  to appear across  $R_G$ .

Figure 3–2. The Noninverting Op Amp

The voltage divider rule is used to calculate  $V_{IN}$ ;  $V_{OUT}$  is the input to the voltage divider, and  $V_{IN}$  is the output of the voltage divider. Since no current can flow into either op amp lead, use of the voltage divider rule is allowed. Equation 3–1 is written with the aid of the voltage divider rule, and algebraic manipulation yields Equation 3–2 in the form of a gain parameter.

$$V_{IN} = V_{OUT} \frac{R_G}{R_G + R_F} \tag{3-1}$$

$$\frac{V_{OUT}}{V_{IN}} = \frac{R_G + R_F}{R_G} = 1 + \frac{R_F}{R_G}$$

(3-2)

When  $R_G$  becomes very large with respect to  $R_F$ ,  $(R_F/R_G) \Rightarrow 0$  and Equation 3–2 reduces to Equation 3–3.

$$V_{OUT} = 1 \tag{3-3}$$

Under these conditions  $V_{OUT} = 1$  and the circuit becomes a unity gain buffer.  $R_G$  is usually deleted to achieve the same results, and when  $R_G$  is deleted,  $R_F$  can also be deleted (RF must be shorted when it is deleted). When  $R_F$  and  $R_G$  are deleted, the op amp output is connected to its inverting input with a wire. Some op amps are self-destructive when  $R_F$  is left out of the circuit, so  $R_F$  is used in many buffer designs. When  $R_F$  is included in a buffer circuit, its function is to protect the inverting input from an over voltage to limit the current through the input ESD (electro-static discharge) structure (typically < 1 mA), and it can have almost any value (20 k is often used).  $R_F$  can never be left out of the circuit

in a current feedback amplifier design because R<sub>F</sub> determines stability in current feedback amplifiers.

Notice that the gain is only a function of the feedback and gain resistors; therefore the feedback has accomplished its function of making the gain independent of the op amp parameters. The gain is adjusted by varying the ratio of the resistors. The actual resistor values are determined by the impedance levels that the designer wants to establish. If  $R_F = 10 \, k$  and  $R_G = 10 \, k$  the gain is two as shown in Equation 2, and if  $R_F = 100 \, k$  and  $R_G = 100 \, k$  the gain is still two. The impedance levels of 10 k or 100 k determine the current drain, the effect of stray capacitance, and a few other points. The impedance level does not set the gain; the ratio of  $R_F/R_G$  does.

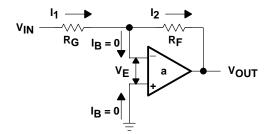

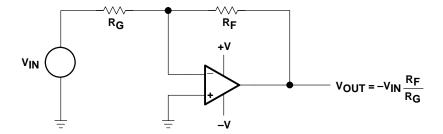

### 3.3 The Inverting Op Amp

The noninverting input of the inverting op amp circuit is grounded. One assumption made is that the input error voltage is zero, so the feedback keeps inverting the input of the op amp at a virtual ground (not actual ground but acting like ground). The current flow in the input leads is assumed to be zero, hence the current flowing through  $R_G$  equals the current flowing through  $R_F$ . Using Kirchoff's law, we write Equation 3–4; and the minus sign is inserted because this is the inverting input. Algebraic manipulation gives Equation 3–5.

Figure 3–3. The Inverting Op Amp

$$I_1 = \frac{V_{IN}}{R_G} = -I_2 = -\frac{V_{OUT}}{R_F}$$

(3-4)

$$\frac{V_{OUT}}{V_{IN}} = -\frac{R_F}{R_G} \tag{3-5}$$

Notice that the gain is only a function of the feedback and gain resistors, so the feedback has accomplished its function of making the gain independent of the op amp parameters. The actual resistor values are determined by the impedance levels that the designer wants to establish. If  $R_F = 10 \, k$  and  $R_G = 10 \, k$  the gain is minus one as shown in Equation

3–5, and if  $R_F = 100$  k and  $R_G = 100$  k the gain is still minus one. The impedance levels of 10 k or 100 k determine the current drain, the effect of stray capacitance, and a few other points. The impedance level does not set the gain; the ratio of  $R_F/R_G$  does.

One final note; the output signal is the input signal amplified and inverted. The circuit input impedance is set by  $R_G$  because the inverting input is held at a virtual ground.

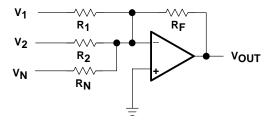

### 3.4 The Adder

An adder circuit can be made by connecting more inputs to the inverting op amp (Figure 3–4). The opposite end of the resistor connected to the inverting input is held at virtual ground by the feedback; therefore, adding new inputs does not affect the response of the existing inputs.

Figure 3-4. The Adder Circuit

Superposition is used to calculate the output voltages resulting from each input, and the output voltages are added algebraically to obtain the total output voltage. Equation 3–6 is the output equation when  $V_1$  and  $V_2$  are grounded. Equations 3–7 and 3–8 are the other superposition equations, and the final result is given in Equation 3–9.

$$V_{OUTN} = -\frac{R_F}{R_N} V_N \tag{3-6}$$

$$V_{OUT1} = -\frac{R_F}{R_1} V_1$$

(3-7)

$$V_{OUT2} = -\frac{R_F}{R_2} V_2$$

(3-8)

$$V_{OUT} = -\left(\frac{R_F}{R_1} V_1 + \frac{R_F}{R_2} V_2 + \frac{R_F}{R_N} V_N\right)$$

(3-9)

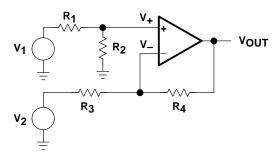

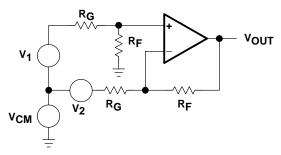

# 3.5 The Differential Amplifier

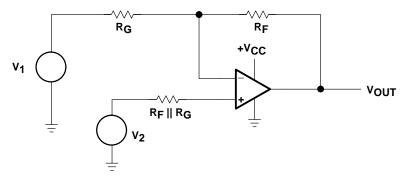

The differential amplifier circuit amplifies the difference between signals applied to the inputs (Figure 3–5). Superposition is used to calculate the output voltage resulting from each input voltage, and then the two output voltages are added to arrive at the final output voltage.

Figure 3-5. The Differential Amplifier

The op amp input voltage resulting from the input source,  $V_1$ , is calculated in Equations 3–10 and 3–11. The voltage divider rule is used to calculate the voltage,  $V_+$ , and the noninverting gain equation (Equation 3–2) is used to calculate the noninverting output voltage,  $V_{OUT1}$ .

$$V_{+} = V_{1} \frac{R_{2}}{R_{1} + R_{2}} \tag{3-10}$$

$$V_{OUT1} = V_{+}(G_{+}) = V_{1} \frac{R_{2}}{R_{1} + R_{2}} \left(\frac{R_{3} + R_{4}}{R_{3}}\right)$$

(3-11)

The inverting gain equation (Equation 3–5) is used to calculate the stage gain for  $V_{OUT2}$  in Equation 3–12. These inverting and noninverting gains are added in Equation 3–13.

$$V_{OUT2} = V_2 \left( -\frac{R_4}{R_3} \right) \tag{3-12}$$

$$V_{OUT} = V_1 \frac{R_2}{R_1 + R_2} \left( \frac{R_3 + R_4}{R_3} \right) - V_2 \frac{R_4}{R_3}$$

(3-13)

When  $R_2 = R_4$  and  $R_1 = R_3$ , Equation 3–13 reduces to Equation 3–14.

$$V_{OUT} = (V_1 - V_2) \frac{R_4}{R_3}$$

(3-14)

It is now obvious that the differential signal,  $(V_1-V_2)$ , is multiplied by the stage gain, so the name differential amplifier suits the circuit. Because it only amplifies the differential

portion of the input signal, it rejects the common-mode portion of the input signal. A common-mode signal is illustrated in Figure 3–6. Because the differential amplifier strips off or rejects the common-mode signal, this circuit configuration is often employed to strip dc or injected common-mode noise off a signal.

Figure 3-6. Differential Amplifier With Common-Mode Input Signal

The disadvantage of this circuit is that the two input impedances cannot be matched when it functions as a differential amplifier, thus there are two and three op amp versions of this circuit specially designed for high performance applications requiring matched input impedances.

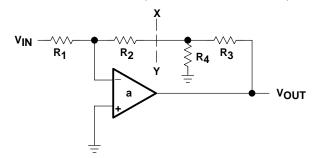

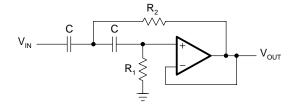

### 3.6 Complex Feedback Networks

When complex networks are put into the feedback loop, the circuits get harder to analyze because the simple gain equations cannot be used. The usual technique is to write and solve node or loop equations. There is only one input voltage, so superposition is not of any use, but Thevenin's theorem can be used as is shown in the example problem given below.

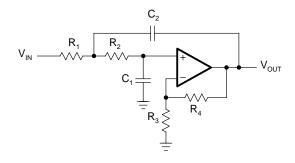

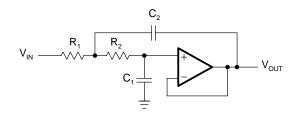

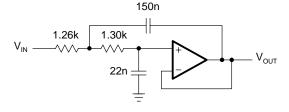

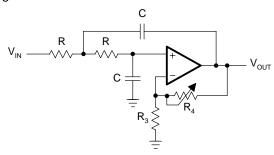

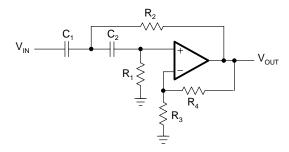

Sometimes it is desirable to have a low resistance path to ground in the feedback loop. Standard inverting op amps can not do this when the driving circuit sets the input resistor value, and the gain specification sets the feedback resistor value. Inserting a *T* network in the feedback loop (Flgure 3–7) yields a degree of freedom that enables both specifications to be met with a low dc resistance path in the feedback loop.

Figure 3-7. T Network in Feedback Loop

Break the circuit at point X–Y, stand on the terminals looking into R<sub>4</sub>, and calculate the Thevenin equivalent voltage as shown in Equation 3–15. The Thevenin equivalent impedance is calculated in Equation 3–16.

$$V_{TH} = V_{OUT} \frac{R_4}{R_3 + R_4}$$

(3-15)

$$R_{TH} = R_3 \parallel R_4 \tag{3-16}$$

Replace the output circuit with the Thevenin equivalent circuit as shown in Figure 5–8, and calculate the gain with the aid of the inverting gain equation as shown in Equation 3–17.

Figure 3–8. Thevenin's Theorem Applied to T Network

Substituting the Thevenin equivalents into Equation 3–17 yields Equation 3–18.

$$-\frac{V_{TH}}{V_{IN}} = \frac{R_2 + R_{TH}}{R_1}$$

(3–17)

$$-\frac{V_{OUT}}{V_{IN}} = \frac{R_2 + R_{TH}}{R_1} \left( \frac{R_3 + R_4}{R_4} \right) = \frac{R_2 + (R_3 \parallel R_4)}{R_1} \left( \frac{R_3 + R_4}{R_4} \right)$$

(3–18)

Algebraic manipulation yields Equation 3–19.

$$-\frac{V_{OUT}}{V_{IN}} = \frac{R_2 + R_3 + \frac{R_2 R_3}{R_4}}{R_1}$$

(3-19)

Specifications for the circuit you are required to build are an inverting amplifier with an input resistance of 10 k ( $R_G = 10 \text{ k}$ ), a gain of 100, and a feedback resistance of 20 K or less. The inverting op amp circuit can not meet these specifications because  $R_F$  must equal 1000 k. Inserting a T network with  $R_2 = R_4 = 10 \text{ k}$  and  $R_3 = 485 \text{ k}$  approximately meets the specifications.

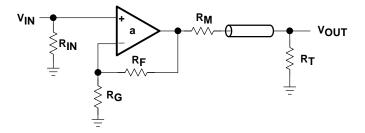

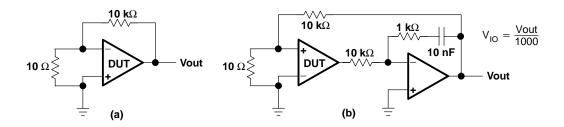

# 3.7 Video Amplifiers

Video signals contain high frequencies, and they use coaxial cable to transmit and receive signals. The cable connecting these circuits has a characteristic impedance of 75  $\Omega$ . To prevent reflections, which cause distortion and ghosting, the input and output circuit impedances must match the 75  $\Omega$  cable.

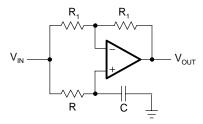

Matching the input impedance is simple for a noninverting amplifier because its input impedance is very high; just make  $R_{IN}$  = 75  $\Omega$ .  $R_F$  and  $R_G$  can be selected as high values, in the hundreds of Ohms range, so that they have minimal affect on the impedance of the input or output circuit. A matching resistor,  $R_M$ , is placed in series with the op amp output to raise its output impedance to 75  $\Omega$ ; a terminating resistor,  $R_T$ , is placed at the input of the next stage to match the cable (Figure 3–9).

Figure 3-9. Video Amplifier

The matching and terminating resistors are equal in value, and they form a voltage divider of 1/2 because  $R_T$  is not loaded. Very often  $R_F$  is selected equal to  $R_G$  so that the op amp gain equals two. Then the system gain, which is the op amp gain multiplied by the divider gain, is equal to one  $(2 \times 1/2 = 1)$ .

### 3.8 Capacitors

Capacitors are a key component in a circuit designer's tool kit, thus a short discussion on evaluating their affect on circuit performance is in order. Capacitors have an impedance of  $X_C = 1/2\pi fC$ . Note that when the frequency is zero the capacitive impedance (also known as reactance) is infinite, and that when the frequency is infinite the capacitive impedance is zero. These end-points are derived from the final value theorem, and they are used to get a rough idea of the effect of a capacitor. When a capacitor is used with a resistor, they form what is called a break-point. Without going into complicated math, just accept that the break frequency occurs at  $f = 1/(2\pi \ RC)$  and the gain is -3 dB at the break frequency.

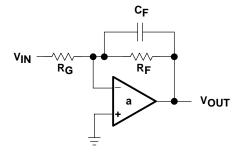

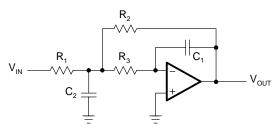

The low pass filter circuit shown in Figure 3–10 has a capacitor in parallel with the feed-back resistor. The gain for the low pass filter is given in Equation 3–20.

Figure 3-10. Low-Pass Filter

$$\frac{V_{OUT}}{V_{IN}} = -\frac{X_C \parallel R_F}{R_G} \tag{3-20}$$

At very low frequencies  $X_C \Rightarrow \infty$ , so  $R_F$  dominates the parallel combination in Equation 20, and the capacitor has no effect. The gain at low frequencies is  $-R_F/R_G$ . At very high frequencies  $X_C \Rightarrow 0$ , so the feedback resistor is shorted out, thus reducing the circuit gain to zero. At the frequency where  $X_C = R_F$  the gain is reduced by  $\sqrt{2}$  because complex impedances in parallel equal half the vector sum of both impedances.

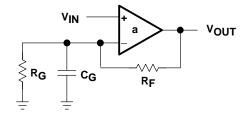

Connecting the capacitor in parallel with  $R_G$  where it has the opposite effect makes a high pass filter (Figure 3–11). Equation 3–21 gives the equation for the high pass filter.

Figure 3–11. High-Pass Filter

$$\frac{V_{OUT}}{V_{IN}} = 1 + \frac{R_F}{X_C \parallel R_G}$$

(3-21)

At very low frequencies  $X_C \Rightarrow \infty$ , so  $R_G$  dominates the parallel combination in Equation 3–21, and the capacitor has no effect. The gain at low frequencies is 1+R<sub>F</sub>/R<sub>G</sub>. At very high frequencies  $X_C \Rightarrow 0$ , so the gain setting resistor is shorted out thus increasing the circuit gain to maximum.

This simple technique is used to predict the form of a circuit transfer function rapidly. Better analysis techniques are presented in later chapters for those applications requiring more precision.

# 3.9 Summary

When the proper assumptions are made, the analysis of op amp circuits is straightforward. These assumptions, which include zero input current, zero input offset voltage, and infinite gain, are realistic assumptions because the new op amps make them true in most applications.

When the signal is comprised of low frequencies, the gain assumption is valid because op amps have very high gain at low frequencies. When CMOS op amps are used, the input current is in the femto amp range; close enough to zero for most applications. Laser trimmed input circuits reduce the input offset voltage to a few micro volts; close enough to zero for most applications. The ideal op amp is becoming real; especially for undemanding applications.

# Single-Supply Op Amp Design Techniques

### Ron Mancini

### 4.1 Single Supply versus Dual Supply

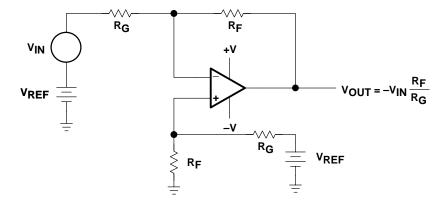

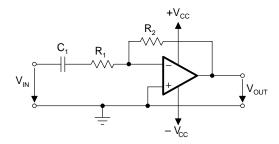

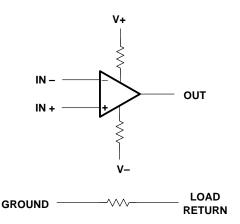

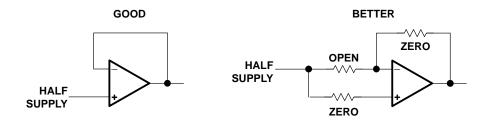

The previous chapter assumed that all op amps were powered from dual or split supplies, and this is not the case in today's world of portable, battery-powered equipment. When op amps are powered from dual supplies (see Figure 4–1), the supplies are normally equal in magnitude, opposing in polarity, and the center tap of the supplies is connected to ground. Any input sources connected to ground are automatically referenced to the center of the supply voltage, so the output voltage is automatically referenced to ground.

Figure 4-1. Split-Supply Op Amp Circuit

Single-supply systems do not have the convenient ground reference that dual-supply systems have, thus biasing must be employed to ensure that the output voltage swings between the correct voltages. Input sources connected to ground are actually connected to a supply rail in single-supply systems. This is analogous to connecting a dual-supply input to the minus power rail. This requirement for biasing the op amp inputs to achieve the desired output voltage swing complicates single-supply designs.

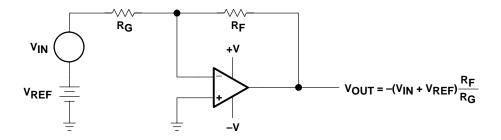

When the signal source is not referenced to ground (see Figure 4–2), the voltage difference between ground and the reference voltage is amplified along with the signal. Unless the reference voltage was inserted as a bias voltage, and such is not the case when the input signal is connected to ground, the reference voltage must be stripped from the signal so that the op amp can provide maximum dynamic range.

Figure 4-2. Split-Supply Op Amp Circuit With Reference Voltage Input

An input bias voltage is used to eliminate the reference voltage when it must not appear in the output voltage (see Figure 4–3). The voltage, V<sub>REF</sub>, is in both input circuits, hence it is named a common-mode voltage. Voltage feedback op amps reject common-mode voltages because their input circuit is constructed with a differential amplifier (chosen because it has natural common-mode voltage rejection capabilities).

Figure 4-3. Split-Supply Op Amp Circuit With Common-Mode Voltage

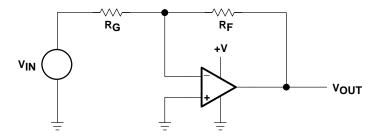

When signal sources are referenced to ground, single-supply op amp circuits exhibit a large input common-mode voltage. Figure 4–4 shows a single-supply op amp circuit that has its input voltage referenced to ground. The input voltage is not referenced to the midpoint of the supplies like it would be in a split-supply application, rather it is referenced to the lower power supply rail. This circuit does not operate when the input voltage is positive because the output voltage would have to go to a negative voltage, hard to do with a positive supply. It operates marginally with small negative input voltages because most op amps do not function well when the inputs are connected to the supply rails.

Figure 4-4. Single-Supply Op Amp Circuit

The constant requirement to account for inputs connected to ground or different reference voltages makes it difficult to design single-supply op amp circuits. Unless otherwise specified, all op amp circuits discussed in this chapter are single-supply circuits. The single-supply may be wired with the negative or positive lead connected to ground, but as long as the supply polarity is correct, the wiring does not affect circuit operation.

Use of a single-supply limits the polarity of the output voltage. When the supply voltage  $V_{CC} = 10 \text{ V}$ , the output voltage is limited to the range  $0 \le V_{out} \le 10$ . This limitation precludes negative output voltages when the circuit has a positive supply voltage, but it does not preclude negative input voltages when the circuit has a positive supply voltage. As long as the voltage on the op amp input leads does not become negative, the circuit can handle negative input voltages.

Beware of working with negative (positive) input voltages when the op amp is powered from a positive (negative) supply because op amp inputs are highly susceptible to reverse voltage breakdown. Also, insure that all possible start-up conditions do not reverse bias the op amp inputs when the input and supply voltage are opposite polarity.

### 4.2 Circuit Analysis

The complexities of single-supply op amp design are illustrated with the following example. Notice that the biasing requirement complicates the analysis by presenting several conditions that are not realizable. It is best to wade through this material to gain an understanding of the problem, especially since a cookbook solution is given later in this chapter. The previous chapter assumed that the op amps were ideal, and this chapter starts to deal with op amp deficiencies. The input and output voltage swing of many op amps are limited as shown in Figure 4–7, but if one designs with the selected rail-to-rail op amps, the input/output swing problems are minimized. The inverting circuit shown in Figure 4–5 is analyzed first.

Figure 4-5. Inverting Op Amp

Equation 4–1 is written with the aid of superposition, and simplified algebraically, to acquire Equation 4–2.

$$V_{OUT} = V_{REF} \left( \frac{R_F}{R_G + R_F} \right) \left( \frac{R_F + R_G}{R_G} \right) - V_{IN} \frac{R_F}{R_G}$$

(4-1)

$$V_{OUT} = (V_{REF} - V_{IN}) \frac{R_F}{R_G}$$

(4-2)

As long as the load resistor,  $R_L$ , is a large value, it does not enter into the circuit calculations, but it can introduce some second order effects such as limiting the output voltage swings. Equation 4–3 is obtained by setting  $V_{REF}$  equal to  $V_{IN}$ , and there is no output voltage from the circuit regardless of the input voltage. The author unintentionally designed a few of these circuits before he created an orderly method of op amp circuit design. Actually, a real circuit has a small output voltage equal to the lower transistor saturation voltage, which is about 150 mV for a TLC07X.

$$V_{OUT} = (V_{REF} - V_{IN}) \frac{R_F}{R_G} = (V_{IN} - V_{IN}) \frac{R_F}{R_G} = 0$$

(4-3)

When  $V_{REF} = 0$ ,  $V_{OUT} = -V_{IN}(R_F/R_G)$ , there are two possible solutions to Equation 4–2. First, when  $V_{IN}$  is any positive voltage,  $V_{OUT}$  should be negative voltage. The circuit can not achieve a negative voltage with a positive supply, so the output saturates at the lower power supply rail. Second, when  $V_{IN}$  is any negative voltage, the output spans the normal range according to Equation 4–5.

$$V_{IN} \ge 0, \qquad V_{OUT} = 0 \tag{4-4}$$

$$V_{IN} \le 0, \qquad V_{OUT} = |V_{IN}| \frac{R_F}{R_G}$$

(4-5)

When  $V_{REF}$  equals the supply voltage,  $V_{CC}$ , we obtain Equation 4–6. In Equation 4–6, when  $V_{IN}$  is negative,  $V_{OUT}$  should exceed  $V_{CC}$ ; that is impossible, so the output saturates. When  $V_{IN}$  is positive, the circuit acts as an inverting amplifier.

$$V_{OUT} = \left(V_{CC} - V_{IN}\right) \frac{R_F}{R_G} \tag{4-6}$$

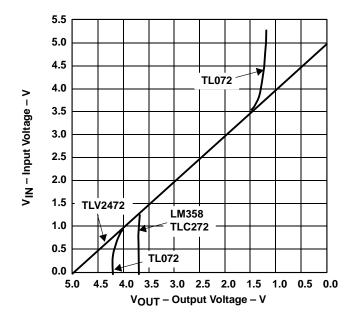

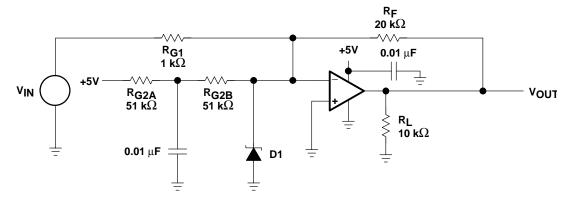

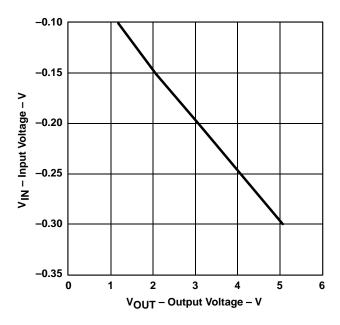

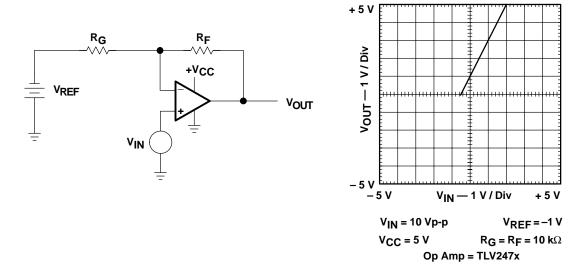

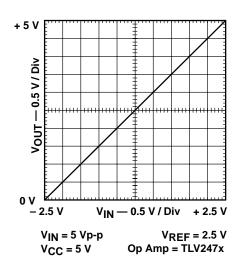

The transfer curve for the circuit shown in Figure 4–6 (VCC = 5 V, RG = RF = 100 k $\Omega$ , RL = 10 k $\Omega$ ) is shown in Figure 4–7.

Figure 4–6. Inverting Op Amp With V<sub>CC</sub> Bias

Figure 4–7. Transfer Curve for Inverting Op Amp With V<sub>CC</sub> Bias

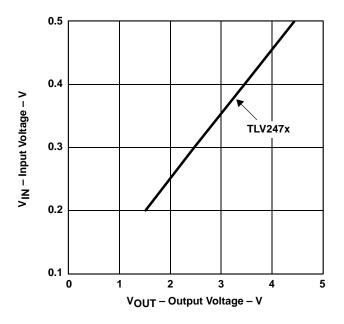

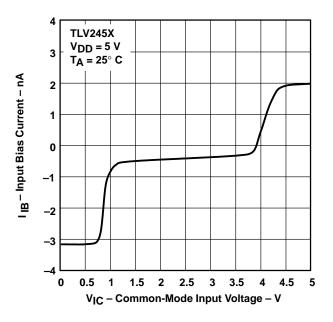

Four op amps were tested in the circuit configuration shown in Figure 4–6. Three of the old generation op amps, LM358, TL07X, and TLC272 had output voltage spans of 2.3 V to 3.75 V. This performance does not justify the ideal op amp assumption that was made in the previous chapter unless the output voltage swing is severely limited. Limited output or input voltage swing is one of the worst deficiencies a single-supply op amp can have because the limited voltage swing limits the circuit's dynamic range. Also, limited voltage swing frequently results in distortion of large signals. The fourth op amp tested was the newer TLV247X, which was designed for rail-to-rail operation in single-supply circuits. The TLV247X plotted a perfect curve (results limited by the instrumentation), and it amazed the author with a textbook performance that justifies the use of ideal assumptions. Some of the older op amps must limit their transfer equation as shown in Equation 4–7.

$$V_{OUT} = (V_{CC} - V_{IN}) \frac{R_F}{R_G}$$

for  $V_{OH} \ge V_{OUT} \ge V_{OL}$  (4-7)

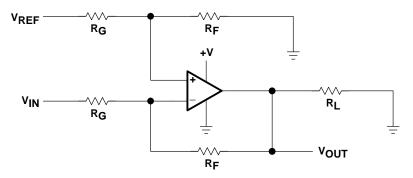

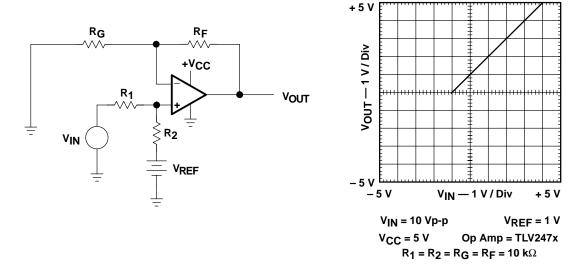

The noninverting op amp circuit is shown in Figure 4–8. Equation 4–8 is written with the aid of superposition, and simplified algebraically, to acquire Equation 4–9.

$$V_{OUT} = V_{IN} \left( \frac{R_F}{R_G + R_F} \right) \left( \frac{R_F + R_G}{R_G} \right) - V_{REF} \frac{R_F}{R_G}$$

(4-8)

$$V_{OUT} = \left(V_{IN} - V_{REF}\right) \frac{R_F}{R_G} \tag{4-9}$$

When  $V_{REF} = 0$ ,  $V_{OUT} = V_{IN} \frac{R_F}{R_G}$ , there are two possible circuit solutions. First, when  $V_{IN}$  is a negative voltage,  $V_{OUT}$  must be a negative voltage. The circuit can not achieve a negative output voltage with a positive supply, so the output saturates at the lower power supply rail. Second, when  $V_{IN}$  is a positive voltage, the output spans the normal range as shown by Equation 4–11.

$$V_{IN} \le 0, \qquad V_{OUT} = 0$$

(4–10)

$$V_{IN} \ge 0, \qquad V_{OUT} = V_{IN}$$

(4-11)

The noninverting op amp circuit is shown in Figure 4–8 with  $V_{CC}$  = 5 V,  $R_G$  =  $R_F$  = 100 k $\Omega$ , and  $R_L$  = 10 k $\Omega$ . The transfer curve for this circuit is shown in Figure 4–9; a TLV247X serves as the op amp.

Figure 4-8. Noninverting Op Amp

Figure 4-9. Transfer Curve for Noninverting Op Amp

There are many possible variations of inverting and noninverting circuits. At this point many designers analyze these variations hoping to stumble upon the one that solves the circuit problem. Rather than analyze each circuit, it is better to learn how to employ simultaneous equations to render specified data into equation form. When the form of the desired equation is known, a circuit that fits the equation is chosen to solve the problem. The resulting equation must be a straight line, thus there are only four possible solutions.

### 4.3 Simultaneous Equations

Taking an orderly path to developing a circuit that works the first time starts here; follow these steps until the equation of the op amp is determined. Use the specifications given for the circuit coupled with simultaneous equations to determine what form the op amp equation must have. Go to the section that illustrates that equation form (called a case), solve the equation to determine the resistor values, and you have a working solution.

A linear op amp transfer function is limited to the equation of a straight line (Equation 4–12).

$$y = \pm mx \pm b \tag{4-12}$$

The equation of a straight line has four possible solutions depending upon the sign of m, the slope, and b, the intercept; thus simultaneous equations yield solutions in four forms. Four circuits must be developed; one for each form of the equation of a straight line. The four equations, cases, or forms of a straight line are given in Equations 4–13 through 4–16, where electronic terminology has been substituted for math terminology.

$$V_{OUT} = + mV_{IN} + b \tag{4-13}$$

$$V_{OLIT} = + mV_{IN} - b \tag{4-14}$$

$$V_{OUT} = -mV_{IN} + b (4-15)$$

$$V_{OUT} = -mV_{IN} - b \tag{4-16}$$

Given a set of two data points for  $V_{OUT}$  and  $V_{IN}$ , simultaneous equations are solved to determine m and b for the equation that satisfies the given data. The sign of m and b determines the type of circuit required to implement the solution. The given data is derived from the specifications; i. e., a sensor output signal ranging from 0.1 V to 0.2 V must be interfaced into an analog-to-digital converter that has an input voltage range of 1 V to 4 V. These data points ( $V_{OUT} = 1 \ V \ @ V_{IN} = 0.1 \ V$ ,  $V_{OUT} = 4 \ V \ @ V_{IN} = 0.2 \ V$ ) are inserted into Equation 4–13, as shown in Equations 4–17 and 4–18, to obtain m and b for the specifications.

$$1 = m(0.1) + b (4-17)$$

$$4 = m(0.2) + b$$

(4–18)

Multiply Equation 4-17 by 2 and subtract it from Equation 4-18.

$$2 = m(0.2) + 2b \tag{4-19}$$

$$b = -2$$

(4–20)

After algebraic manipulation of Equation 4–17, substitute Equation 4–20 into Equation 4–17 to obtain Equation 4–21.

$$m = \frac{2+1}{0.1} = 30 \tag{4-21}$$

Now m and b are substituted back into Equation 4-13 yielding Equation 4-22.

$$V_{OLIT} = 30V_{IN} - 2$$

(4–22)

Notice, although Equation 4–13 was the starting point, the form of Equation 4–22 is identical to the format of Equation 4–14. The specifications or given data determine the sign of m and b, and starting with Equation 4–13, the final equation form is discovered after m and b are calculated. The next step required to complete the problem solution is to develop a circuit that has an m = 30 and b = -2. Circuits were developed for Equations 4–13 through 4–16, and they are given under the headings Case 1 through Case 4 respectively. There are different circuits that will yield the same equations, but these circuits were selected because they do not require negative references.

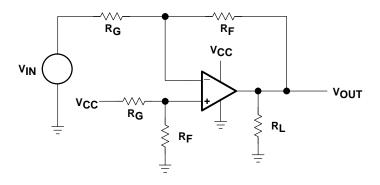

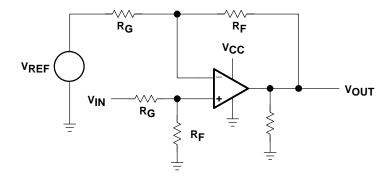

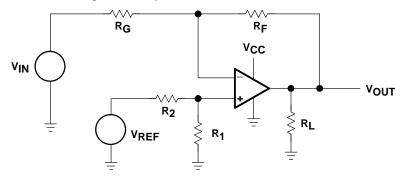

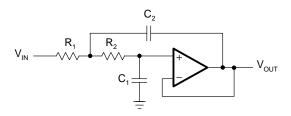

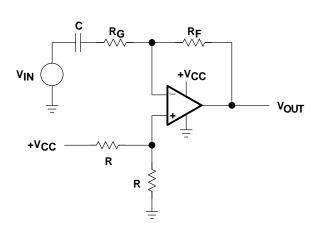

### 4.3.1 Case 1: $V_{OUT} = +mV_{IN}+b$

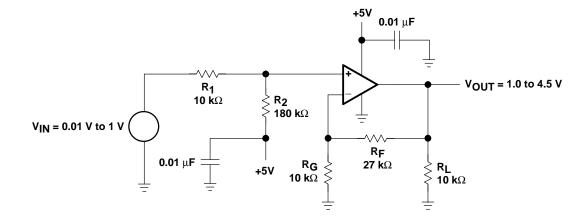

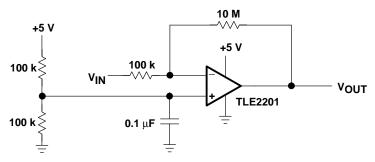

The circuit configuration that yields a solution for Case 1 is shown in Figure 4–10. The figure includes two 0.01- $\mu$ F capacitors. These capacitors are called decoupling capacitors, and they are included to reduce noise and provide increased noise immunity. Sometimes two 0.01- $\mu$ F capacitors serve this purpose, sometimes more extensive filtering is needed, and sometimes one capacitor serves this purpose. Special attention must be paid to the regulation and noise content of  $V_{CC}$  when  $V_{CC}$  is used as a reference because some portion of the noise content of  $V_{CC}$  will be multiplied by the circuit gain

Figure 4–10. Schematic for Case1:  $V_{OUT} = +mV_{IN} + b$

The circuit equation is written using the voltage divider rule and superposition.

$$V_{OUT} = V_{IN} \left( \frac{R_2}{R_1 + R_2} \right) \left( \frac{R_F + R_G}{R_G} \right) + V_{REF} \left( \frac{R_1}{R_1 + R_2} \right) \left( \frac{R_F + R_G}{R_G} \right)$$

(4-23)

The equation of a straight line (case 1) is repeated in Equation 4–24 below so comparisons can be made between it and Equation 4–23.

$$V_{OUT} = mV_{IN} + b \tag{4-24}$$

Equating coefficients yields Equations 4-25 and 4-26.

$$m = \left(\frac{R_2}{R_1 + R_2}\right) \left(\frac{R_F + R_G}{R_G}\right) \tag{4-25}$$

$$b = V_{REF} \left( \frac{R_1}{R_1 + R_2} \right) \left( \frac{R_F + R_G}{R_G} \right)$$

(4–26)

Example; the circuit specifications are  $V_{OUT} = 1 \text{ V}$  at  $V_{IN} = 0.01 \text{ V}$ ,  $V_{OUT} = 4.5 \text{ V}$  at  $V_{IN} = 1 \text{ V}$ ,  $R_L = 10 \text{ k}$ , five percent resistor tolerances, and  $V_{CC} = 5 \text{ V}$ . No reference voltage is available, thus  $V_{CC}$  is used for the reference input, and  $V_{REF} = 5 \text{ V}$ . A reference voltage source is left out of the design as a space and cost savings measure, and it sacrifices noise performance, accuracy, and stability performance. Cost is an important specification, but the  $V_{CC}$  supply must be specified well enough to do the job. Each step in the subsequent design procedure is included in this analysis to ease learning and increase boredom. Many steps are skipped when subsequent cases are analyzed.

The data is substituted into simultaneous equations.

$$1 = m(0.01) + b (4-27)$$

$$4.5 = m(1.0) + b$$

(4–28)

Equation 4–27 is multiplied by 100 (Equation 4–29) and Equation 4–28 is subtracted from Equation 4–29 to obtain Equation 4–30.

$$100 = m(1.0) + 100b (4-29)$$

$$b = \frac{95.5}{99} = 0.9646 \tag{4-30}$$

The slope of the transfer function, m, is obtained by substituting b into Equation 4–27.

$$m = \frac{1-b}{0.01} = \frac{1-0.9646}{0.01} = 3.535 \tag{4-31}$$

Now that b and m are calculated, the resistor values can be calculated. Equations 4-25 and 4-26 are solved for the quantity  $(R_F + R_G)/R_G$ , and then they are set equal in Equation 4-32 thus yielding Equation 4-33.

$$\frac{R_{F} + R_{G}}{R_{G}} = m \left( \frac{R_{1} + R_{2}}{R_{2}} \right) = \frac{b}{V_{CC}} \left( \frac{R_{1} + R_{2}}{R_{1}} \right)$$

(4-32)

$$R_2 = \frac{3.535}{0.9646} R_1 = 18.316 R_1 \tag{4-33}$$

Five percent tolerance resistors are specified for this design, so we choose  $R_1$  = 10 k $\Omega$ , and that sets the value of  $R_2$  = 183.16 k $\Omega$ . The closest 5% resistor value to 183.16 k $\Omega$  is 180 k $\Omega$ ; therefore, select  $R_1$  = 10 k $\Omega$  and  $R_2$  = 180 k $\Omega$ . Being forced to yield to reality by choosing standard resistor values means that there is an error in the circuit transfer function because m and b are not exactly the same as calculated. The real world constantly forces compromises into circuit design, but the good circuit designer accepts the challenge and throws money or brains at the challenge. Resistor values closer to the calculated values could be selected by using 1% or 0.5% resistors, but that selection increases cost and violates the design specification. The cost increase is hard to justify except in precision circuits. Using ten-cent resistors with a ten-cent op amp usually is false economy.

The left half of Equation 4–32 is used to calculate R<sub>F</sub> and R<sub>G</sub>.

$$\frac{R_F + R_G}{R_G} = m \left( \frac{R_1 + R_2}{R_2} \right) = 3.535 \left( \frac{180 + 10}{180} \right) = 3.73 \tag{4-34}$$

$$R_{F} = 2.73R_{G}$$

(4–35)

The resulting circuit equation is given below.

$$V_{OUT} = 3.5V_{IN} + 0.97$$

(4–36)

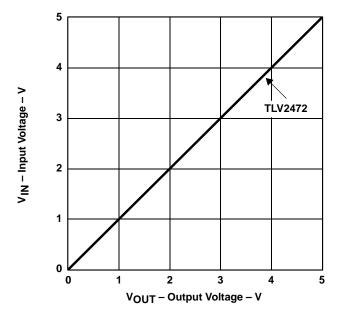

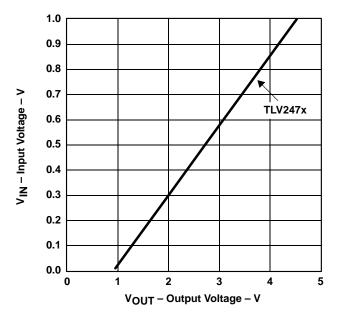

The gain setting resistor,  $R_G$ , is selected as 10 k $\Omega$ , and 27 k $\Omega$ , the closest 5% standard value is selected for the feedback resistor,  $R_F$ . Again, there is a slight error involved with standard resistor values. This circuit must have an output voltage swing from 1 V to 4.5 V. The older op amps can not be used in this circuit because they lack dynamic range, so the TLV247X family of op amps is selected. The data shown in Figure 4–7 confirms the op amp selection because there is little error. The circuit with the selected component values is shown in Figure 4–11. The circuit was built with the specified components, and the transfer curve is shown in Figure 4–12.

Figure 4-11. Case 1 Example Circuit

Figure 4-12. Case 1 Example Circuit Measured Transfer Curve

The transfer curve shown is a straight line, and that means that the circuit is linear. The  $V_{OUT}$  intercept is about 0.98 V rather than 1 V as specified, and this is excellent performance considering that the components were selected randomly from bins of resistors. Different sets of components would have slightly different slopes because of the resistor tolerances. The TLV247X has input bias currents and input offset voltages, but the effect of these errors is hard to measure on the scale of the output voltage. The output voltage

measured 4.53 V when the input voltage was 1 V. Considering the low and high input voltage errors, it is safe to conclude that the resistor tolerances have skewed the gain slightly, but this is still excellent performance for 5% components. Often lab data similar to that shown here is more accurate than the 5% resistor tolerance, but do not fall into the trap of expecting this performance, because you will be disappointed if you do.

The resistors were selected in the k- $\Omega$  range arbitrarily. The gain and offset specifications determine the resistor ratios, but supply current, frequency response, and op amp drive capability determine their absolute values. The resistor value selection in this design is high because modern op amps do not have input current offset problems, and they yield reasonable frequency response. If higher frequency response is demanded, the resistor values must decrease, and resistor value decreases reduce input current errors, while supply current increases. When the resistor values get low enough, it becomes hard for another circuit, or possibly the op amp, to drive the resistors.

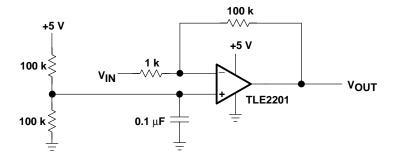

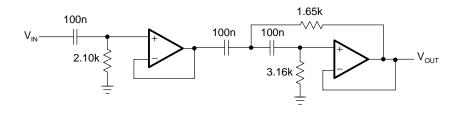

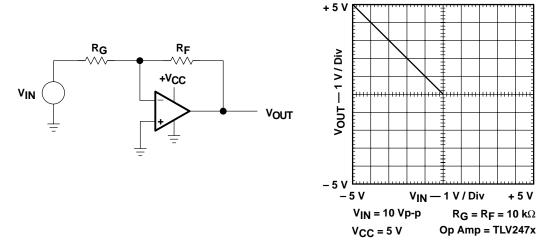

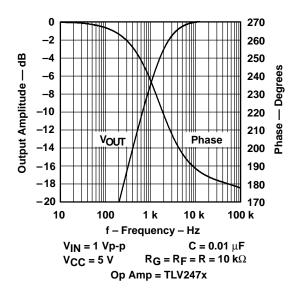

#### 4.3.2 Case 2: $V_{OUT} = +mV_{IN} - b$

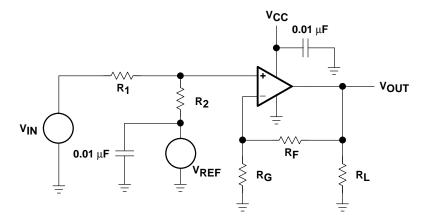

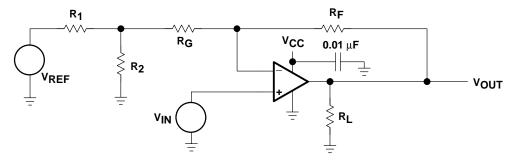

The circuit shown in Figure 4–13 yields a solution for Case 2. The circuit equation is obtained by taking the Thevenin equivalent circuit looking into the junction of  $R_1$  and  $R_2$ . After the  $R_1$ ,  $R_2$  circuit is replaced with the Thevenin equivalent circuit, the gain is calculated with the ideal gain equation (Equation 4–37).

Figure 4–13. Schematic for Case 2:  $V_{OUT} = +mV_{IN-b}$

$$V_{OUT} = V_{IN} \left( \frac{R_F + R_G + R_1 \parallel R_2}{R_G + R_1 \parallel R_2} \right) - V_{REF} \left( \frac{R_2}{R_1 + R_2} \right) \left( \frac{R_F}{R_G + R_1 \parallel R_2} \right)$$

(4-37)

Comparing terms in Equations 4–37 and 4–14 enables the extraction of m and b.

$$m = \frac{R_F + R_G + R_1 \parallel R_2}{R_G + R_1 \parallel R_2}$$

(4–38)

$$|b| = V_{REF} \left( \frac{R_2}{R_1 + R_2} \right) \left( \frac{R_F}{R_G + R_1 \parallel R_2} \right)$$

(4-39)

The specifications for an example design are:  $V_{OUT}$  = 1.5 V @  $V_{IN}$  = 0.2 V,  $V_{OUT}$  = 4.5 V @  $V_{IN}$  = 0.5 V,  $V_{REF}$  =  $V_{CC}$  = 5 V,  $R_L$  = 10 k $\Omega$ , and 5% resistor tolerances. The simultaneous equations, (Equations 4–40 and 4–41), are written below.

$$1.5 = 0.2m + b \tag{4-40}$$

$$4.5 = 0.5 \text{m} + \text{b}$$

(4–41)

From these equations we find that b = -0.5 and m = 10. Making the assumption that  $R_1 || R_2 << R_G$  simplifies the calculations of the resistor values.

$$m = 10 = \frac{R_F + R_G}{R_G}$$

(4–42)

$$R_{F} = 9R_{G} \tag{4-43}$$

Let  $R_G = 20 \text{ k}\Omega$ , and then  $R_F = 180 \text{ k}\Omega$ .

$$b = V_{CC} \left( \frac{R_F}{R_G} \right) \left( \frac{R_2}{R_1 + R_2} \right) = 5 \left( \frac{180}{20} \right) \left( \frac{R_2}{R_1 + R_2} \right)$$

(4-44)

$$R_1 = \frac{1 - 0.01111}{0.01111} R_2 = 89R_2 \tag{4-45}$$

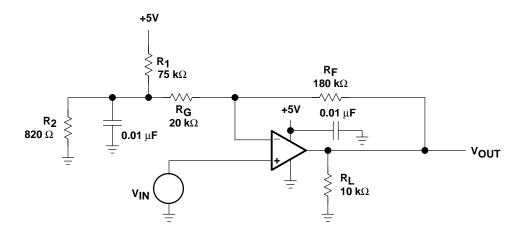

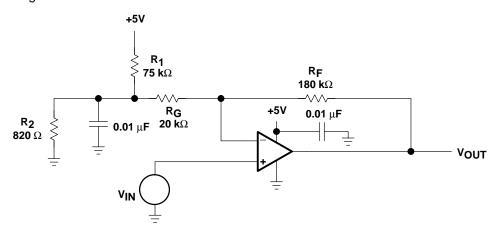

Select  $R_2$  = 0.82 k $\Omega$  and  $R_1$  equals 72.98 k $\Omega$ . Since 72.98 k $\Omega$  is not a standard 5% resistor value,  $R_1$  is selected as 75 k $\Omega$ . The difference between the selected and calculated value of  $R_1$  has about a 3% effect on b, and this error shows up in the transfer function as an intercept rather than a slope error. The parallel resistance of  $R_1$  and  $R_2$  is approximately 0.82 k $\Omega$  and this is much less than  $R_G$ , which is 20 k $\Omega$ , thus the earlier assumption that  $R_G >> R1 || R2$  is justified.  $R_2$  could have been selected as a smaller value, but the smaller values yielded poor standard 5% values for  $R_1$ . The final circuit is shown in Figure 4–14 and the measured transfer curve for this circuit is shown in Figure 4–15.

Figure 4-14. Case 2 Example Circuit

Figure 4-15. Case 2 Example Circuit Measured Transfer Curve

The TLV247X was used to build the test circuit because of its wide dynamic range. The transfer curve plots very close to the theoretical curve; the direct result of using a high performance op amp.

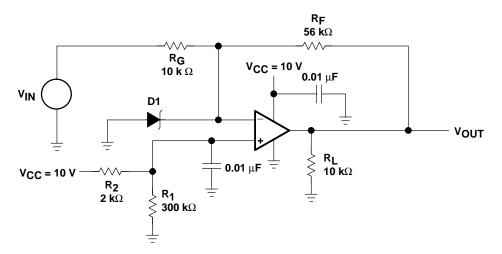

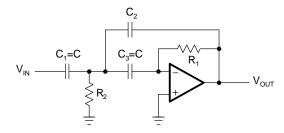

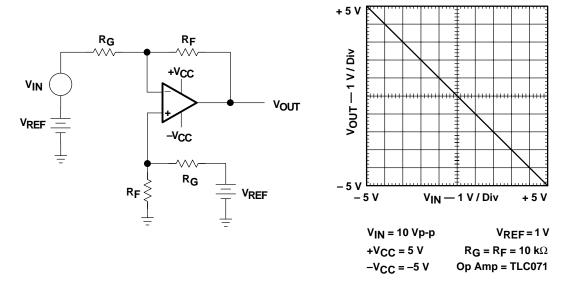

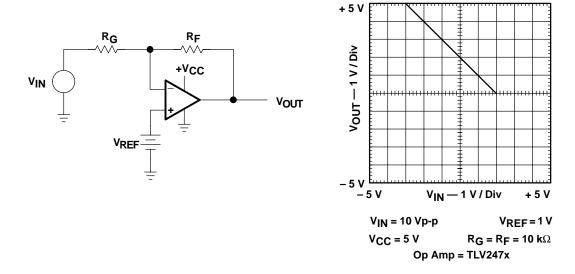

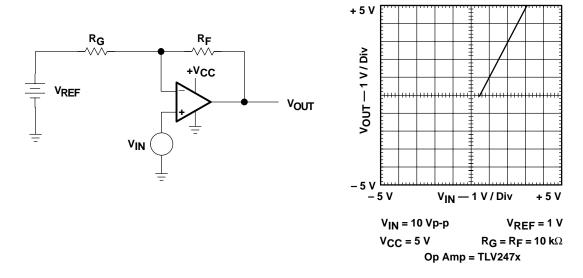

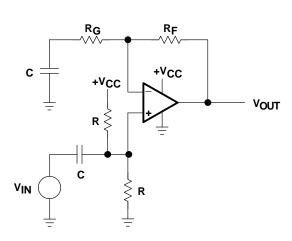

#### 4.3.3 Case 3: $V_{OUT} = -mV_{IN} + b$

The circuit shown in Figure 4–16 yields the transfer function desired for Case 3.

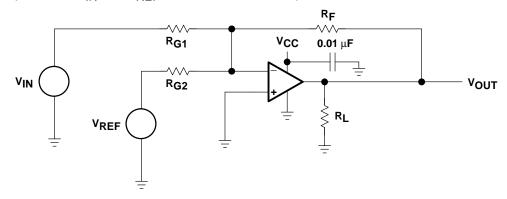

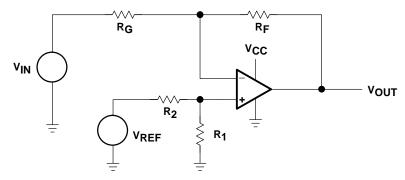

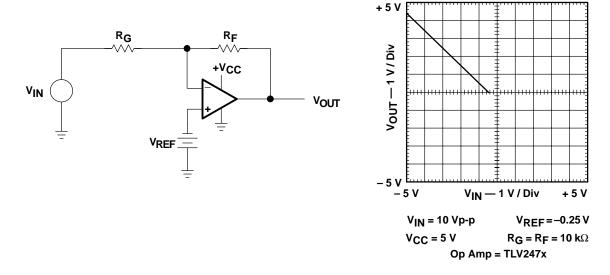

Figure 4–16. Schematic for Case 3:  $V_{OUT} = -mV_{IN} + b$

The circuit equation is obtained with superposition.

$$V_{OUT} = -V_{IN} \left(\frac{R_F}{R_G}\right) + V_{REF} \left(\frac{R_1}{R_1 + R_2}\right) \left(\frac{R_F + R_G}{R_G}\right)$$

(4-46)

Comparing terms between Equations 4–45 and 4–15 enables the extraction of m and b.

$$|\mathsf{m}| = \frac{\mathsf{R}_{\mathsf{F}}}{\mathsf{R}_{\mathsf{G}}} \tag{4-47}$$

$$b = V_{REF} \left( \frac{R_1}{R_1 + R_2} \right) \left( \frac{R_F + R_G}{R_G} \right)$$

(4-48)

The design specifications for an example circuit are:  $V_{OUT} = 1 \ V \ @ V_{IN} = -0.1 \ V$ ,  $V_{OUT} = 6 \ V \ @ V_{IN} = -1 \ V$ ,  $V_{REF} = V_{CC} = 10 \ V$ ,  $R_L = 100 \ \Omega$ , and 5% resistor tolerances. The supply voltage available for this circuit is 10 V, and this exceeds the maximum allowable supply voltage for the TLV247X. Also, this circuit must drive a back-terminated cable that looks like two  $50-\Omega$  resistors connected in series, thus the op amp must be able to drive  $6/100 = 60 \ mA$ . The stringent op amp selection criteria limits the choice to relatively new op amps if ideal op amp equations are going to be used. The TLC07X has excellent single-supply input performance coupled with high output current drive capability, so it is selected for this circuit. The simultaneous equations (Equations 4–49 and 4–50), are written below.

$$1 = (-0.1)m + b (4-49)$$

$$6 = (-1)m + b$$

(4–50)

From these equations we find that b = 0.444 and m = -5.6.

$$|\mathbf{m}| = 5.56 = \frac{R_{F}}{R_{G}} \tag{4-51}$$

$$R_{F} = 5.56R_{G}$$

(4–52)

Let  $R_G$  = 10 k $\Omega$ , and then  $R_F$  = 56.6 k $\Omega$ , which is not a standard 5% value, hence  $R_F$  is selected as 56 k $\Omega$ .

$$b = V_{CC} \left( \frac{R_F + R_G}{R_G} \right) \left( \frac{R_1}{R_1 + R_2} \right) = 10 \left( \frac{56 + 10}{10} \right) \left( \frac{R_1}{R_1 + R_2} \right)$$

(4-53)

$$R_2 = \frac{66 - 0.4444}{0.4444} R_1 = 147.64 R_1 \tag{4-54}$$

The final equation for the example is given below

$$V_{OLIT} = -5.56V_{IN} + 0.444 \tag{4-55}$$

Select  $R_1 = 2 \, k\Omega$  and  $R_2 = 295.28 \, k\Omega$ . Since  $295.28 \, k\Omega$  is not a standard 5% resistor value,  $R_1$  is selected as 300  $k\Omega$ . The difference between the selected and calculated value of  $R_1$  has a nearly insignificant effect on b. The final circuit is shown in Figure 4–17, and the measured transfer curve for this circuit is shown in Figure 4–18.

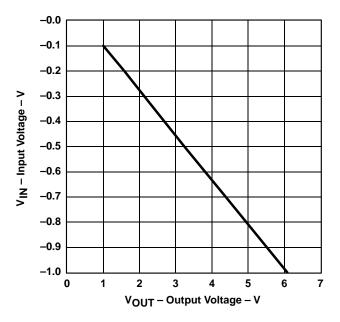

Figure 4-17. Case 3 Example Circuit

Figure 4–18. Case 3 Example Circuit Measured Transfer Curve

As long as the circuit works normally, there are no problems handling the negative voltage input to the circuit, because the inverting lead of the TLC07X is at a positive voltage. The positive op amp input lead is at a voltage of approximately 65 mV, and normal op amp operation keeps the inverting op amp input lead at the same voltage because of the assumption that the error voltage is zero. When  $V_{CC}$  is powered down while there is a negative voltage on the input circuit, most of the negative voltage appears on the inverting op amp input lead.

The most prudent solution is to connect the diode,  $D_1$ , with its cathode on the inverting op amp input lead and its anode at ground. If a negative voltage gets on the inverting op amp input lead, it is clamped to ground by the diode. Select the diode type as germanium or Schottky so the voltage drop across the diode is about 200 mV; this small voltage does not harm most op amp inputs. As a further precaution,  $R_G$  can be split into two resistors with the diode inserted at the junction of the two resistors. This places a current limiting resistor between the diode and the inverting op amp input lead.

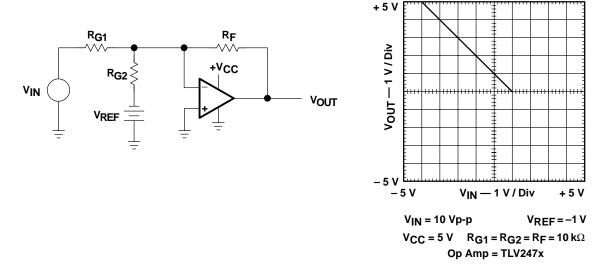

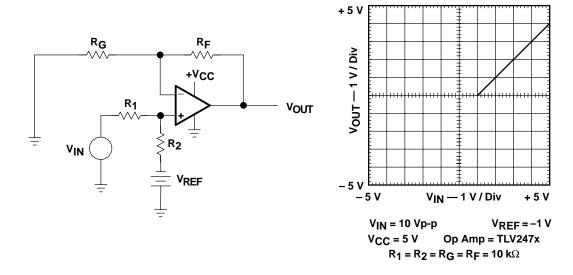

#### 4.3.4 Case 4: $V_{OUT} = -mV_{IN} - b$

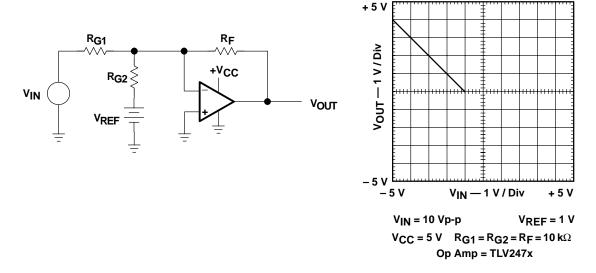

The circuit shown in Figure 4–19 yields a solution for Case 4. The circuit equation is obtained by using superposition to calculate the response to each input. The individual responses to  $V_{\rm IN}$  and  $V_{\rm REF}$  are added to obtain Equation 4–56.

Figure 4–19. Schematic for Case 4:  $V_{OUT} = -mV_{IN} - b$

$$V_{OUT} = -V_{IN} \frac{R_F}{R_{G1}} - V_{REF} \frac{R_F}{R_{G2}}$$

(4–56)

Comparing terms in Equations 4–56 and 4–16 enables the extraction of m and b.

$$|\mathsf{m}| = \frac{\mathsf{R}_{\mathsf{F}}}{\mathsf{R}_{\mathsf{G1}}} \tag{4-57}$$

$$|\mathbf{b}| = V_{REF} \frac{R_F}{R_{G2}} \tag{4-58}$$

The design specifications for an example circuit are:  $V_{OUT}$  = 1 V @  $V_{IN}$  = -0.1 V,  $V_{OUT}$  = 5 V @  $V_{IN}$  =-0.3 V,  $V_{REF}$  =  $V_{CC}$  = 5 V,  $R_L$  = 10 k $\Omega$ , and 5% resistor tolerances. The simultaneous Equations 4–59 and 4–60, are written below.

$$1 = (-0.1)m + b (4-59)$$

$$5 = (-0.3)m + b$$

(4-60)

From these equations we find that b = -1 and m = -20. Setting the magnitude of m equal to Equation 4–57 yields Equation 4–61.

$$|\mathbf{m}| = 20 = \frac{R_{F}}{R_{G1}} \tag{4-61}$$

$$R_{F} = 20R_{G1}$$

(4–62)

Let  $R_{G1} = 1 \text{ k}\Omega$ , and then  $R_F = 20 \text{ k}\Omega$ .

$$|b| = V_{CC} \left(\frac{R_F}{R_{G1}}\right) = 5 \left(\frac{R_F}{R_{G2}}\right) = 1$$

(4-63)

$$R_{G2} = \frac{R_F}{0.2} = \frac{20}{0.2} = 100 \text{ k}\Omega$$

(4-64)

The final equation for this example is given in Equation 4-63.

$$V_{OUT} = -20V_{IN} - 1$$

(4-65)

The final circuit is shown in Figure 4–20 and the measured transfer curve for this circuit is shown in Figure 4–21.

Figure 4-20. Case 4 Example Circuit

Figure 4–21. Case 4 Example Circuit Measured Transfer Curve

The TLV247X was used to build the test circuit because of its wide dynamic range. The transfer curve plots very close to the theoretical curve, and this results from using a high performance op amp.

As long as the circuit works normally there are no problems handling the negative voltage input to the circuit because the inverting lead of the TLV247X is at a positive voltage. The positive op amp input lead is grounded, and normal op amp operation keeps the inverting op amp input lead at ground because of the assumption that the error voltage is zero. When  $V_{CC}$  is powered down while there is a negative voltage on the inverting op amp input lead.